ICdesign Log

Published:

intro: USTC_2022FA Course

Plan

芯片设计实践(EE4001.01) advisor: Xuefei Bai

项目计划:在TSMC 180nm工艺下设计SoC,包括mips cpu,脉动阵列加速器,外部接口,整个项目使用Synopsys EDA套件完成(Design complier,IC compiler)

Systolic Array Specification

- 由于mips 8bit,寻址空间不是很大,和空间因素,所以阵列大小限制为4*4

- 4*4矩阵两个,需要32个连续地址,所以用addr[6]区别源数据域和其他域,addr[7]区别结果域和指令域。

- 由于寄存器过小,需要一个DMA来转移数据

- 数据准备区需要和DMA联合,形成FSM来保证数据准备完毕和计算完毕

- 全部采用流水化,短连线的方式。

- DMA采用简单时序,时间长些没关系。

DMA+准备区规格:

- 准备区有AB两个,大小为7*4的移位寄存器阵列。

- DMA一次顺序访存一行4*2个数,然后交由准备区后进行下一次访存,一切由控制器控制。

- 要求一次对每个矩阵的每一单元同时load一个元素,则带宽是 8unit/clk

- A矩阵的物理存储排布是关于竖直轴对称,B矩阵的物理存储排布是关于水平轴对称

- 在ram里最好是A列优先,B行优先,这样是连续取址的

PE规格:

- 采用A、B矩阵流入,输出固定的方法,在最后提取输出到缓存区

- 8bitMAC

控制器时序:

- mips单设一个指令SAC(systolic array computing),从本周期开始cpu stall,协处理器收到信号开始在固定的访存地址上访存,需要的clock取决于sram访存方式,如果可以并行的话就更快。

- 直到A、B的数据都已经准备完毕以后,开始流水计算工作,这个需要固定的12clk以确保计算完毕(用4bit定时器)。

- 开始移位输出到缓冲区,需要4clk,需要访存stall功能。

- DMA传输回sram。

面积预估:

宽约为 (7+4) * l(reg) + 4 * l(PE) = ((7 + 4) * 4 + 4 * 30) * 3.92um = 635um 高约为 4h(PE)+7l(reg) = (4 * 60 + 7 * 4)*3.92um = 1050 mm 面积约为 0.6mm^2 (极为保守估计,无任何优化)

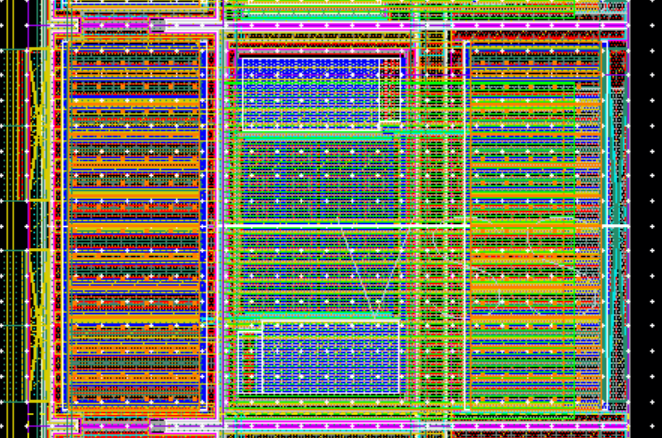

Snapshot

仿真阶段

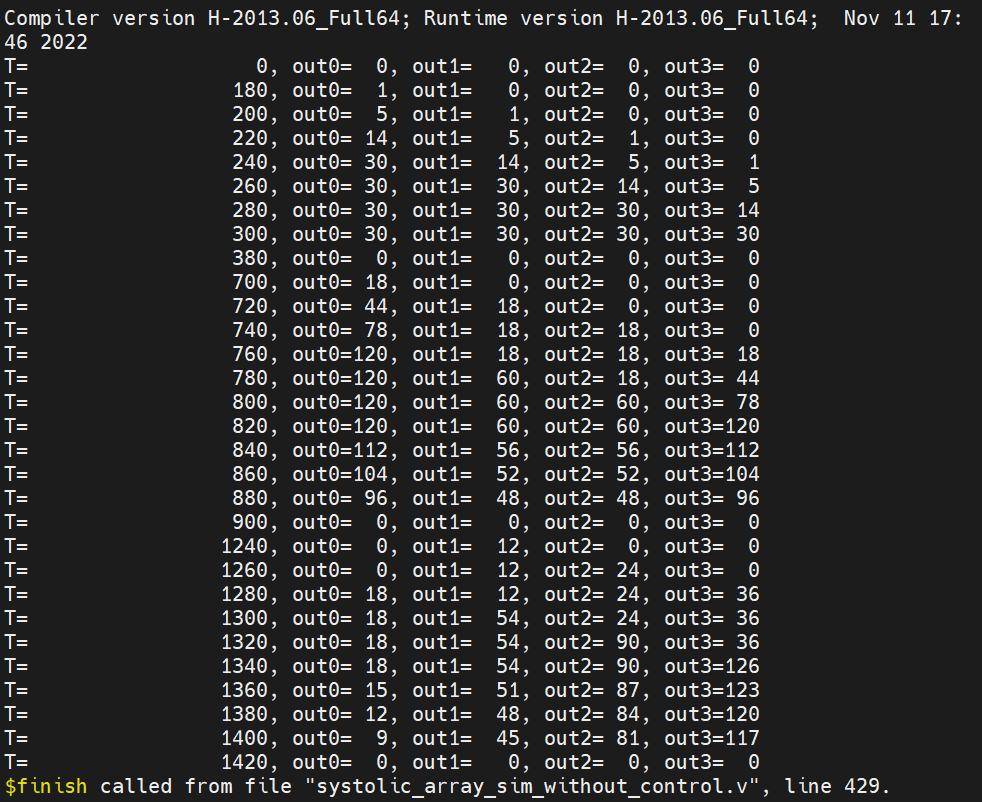

无FSM控制仿真:

样例:C=AB F=DE I=GH

- A = { 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 } B = { 1 1 1 1 2 2 2 2 3 3 3 3 4 4 4 4 } C = { 30 30 30 30 30 30 30 30 30 30 30 30 30 30 30 30 }

- D = { 1 1 1 1 1 0 0 1 1 0 0 1 1 1 1 1 } E = { 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 } F = { 96 104 112 120 48 52 56 60 48 52 56 60 96 104 112 120 }

- G = { 0 3 6 9 12 15 18 21 24 27 30 33 36 39 42 45 }

H = { 2 0 0 1 0 2 1 0 0 1 2 0 1 0 0 2 }

I = { 9 12 15 18 45 48 51 54 81 84 87 90 117 120 123 126 }

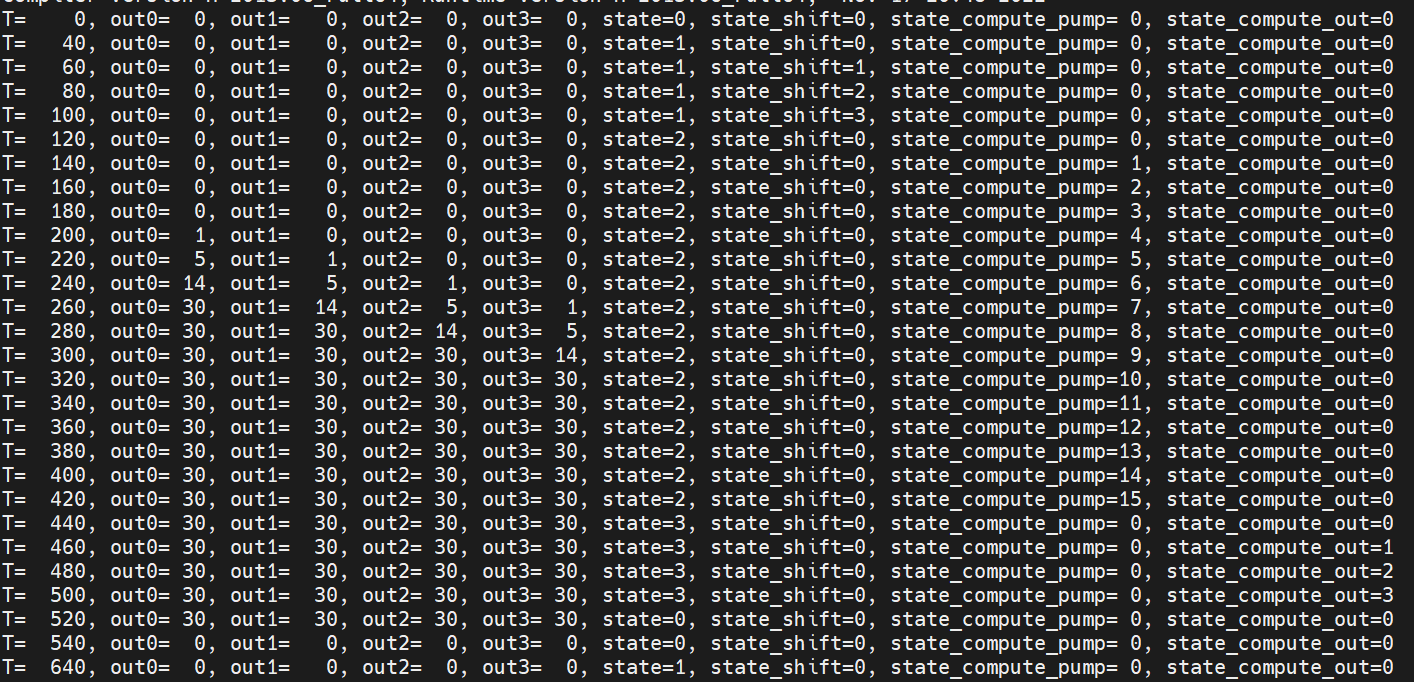

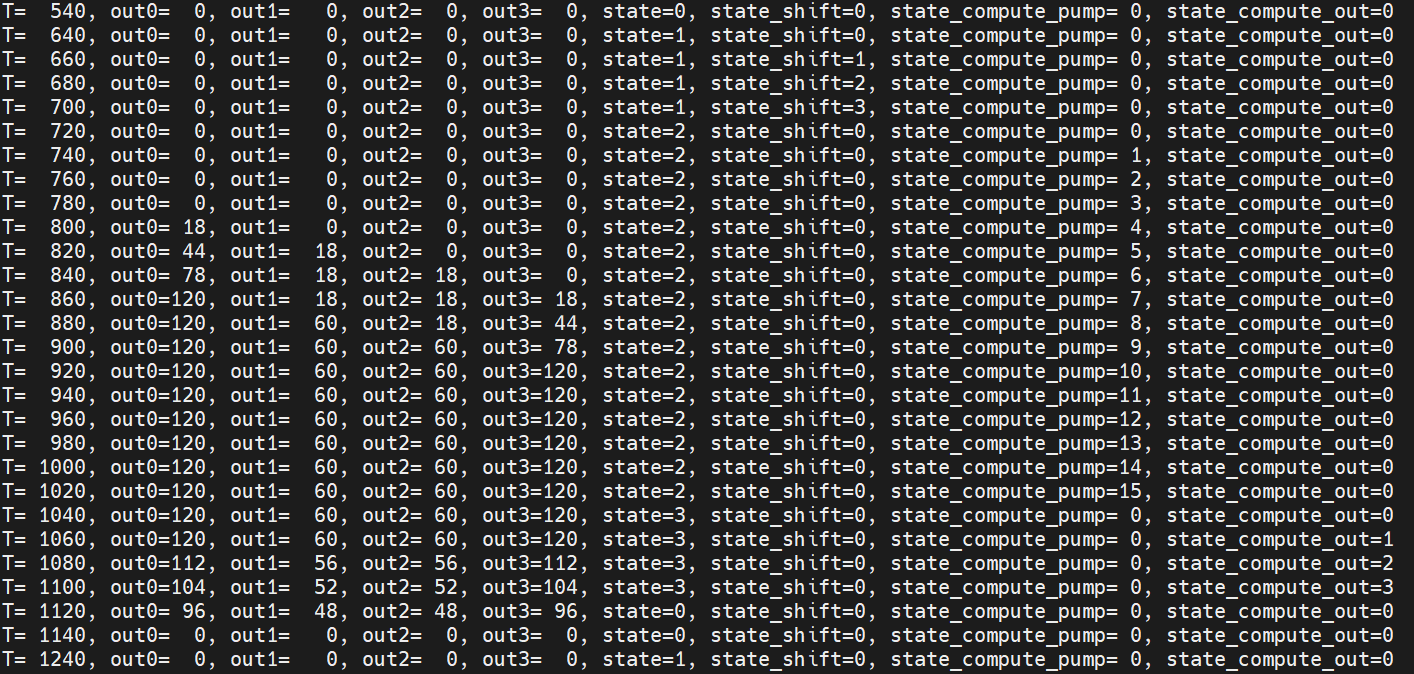

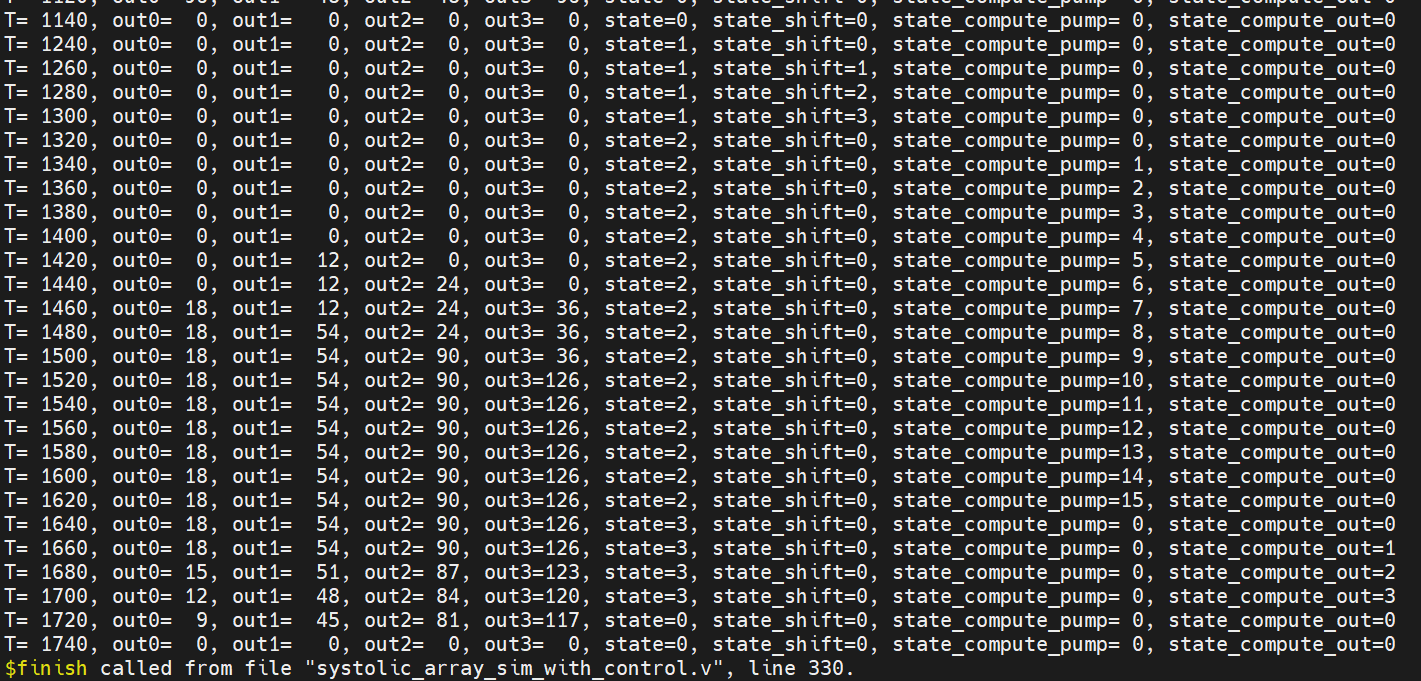

有FSM controller仿真:

综合阶段

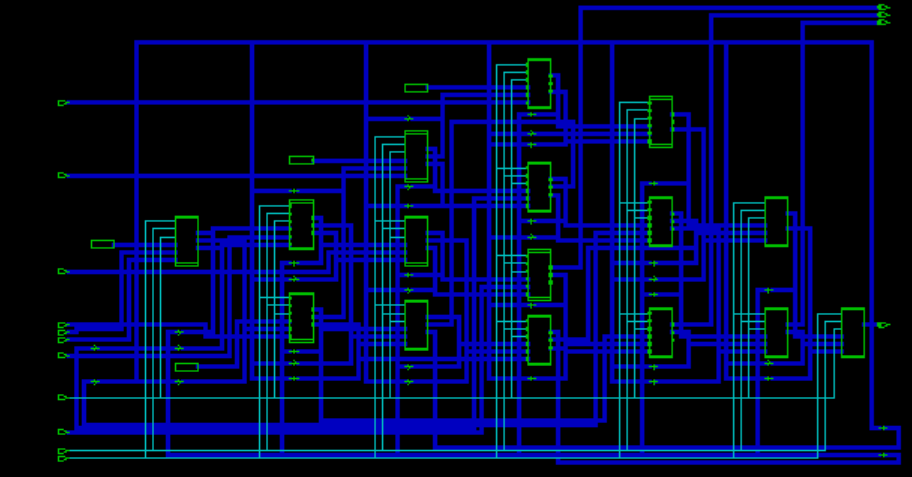

systolic array (4x4) schematic:

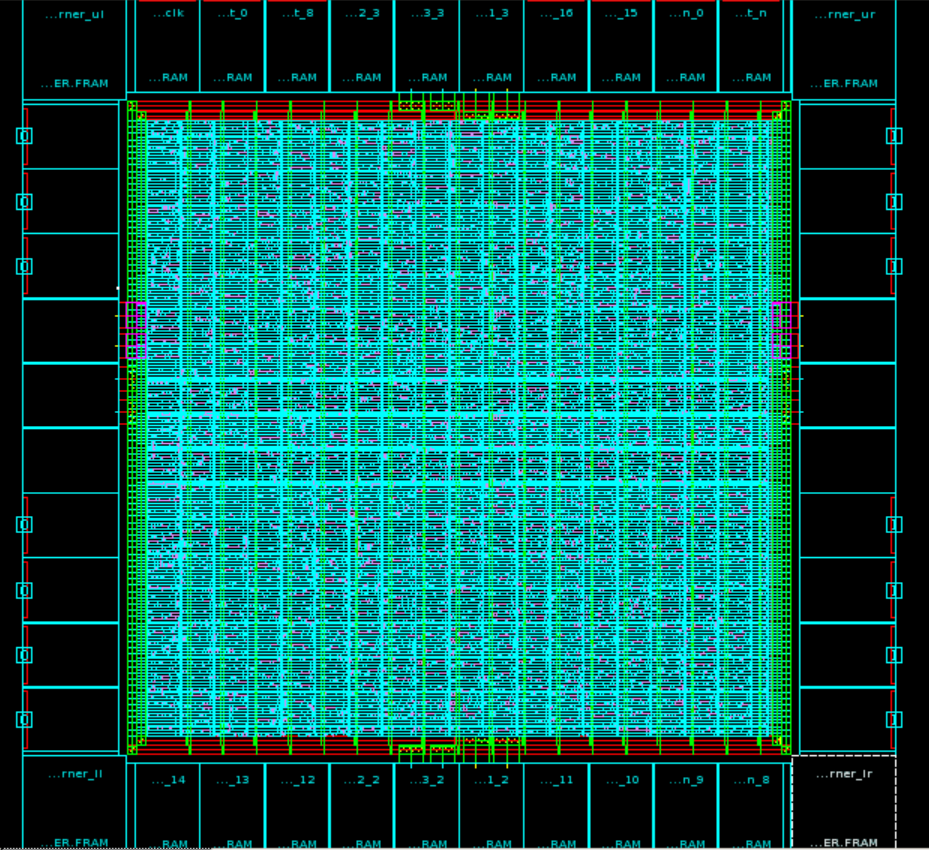

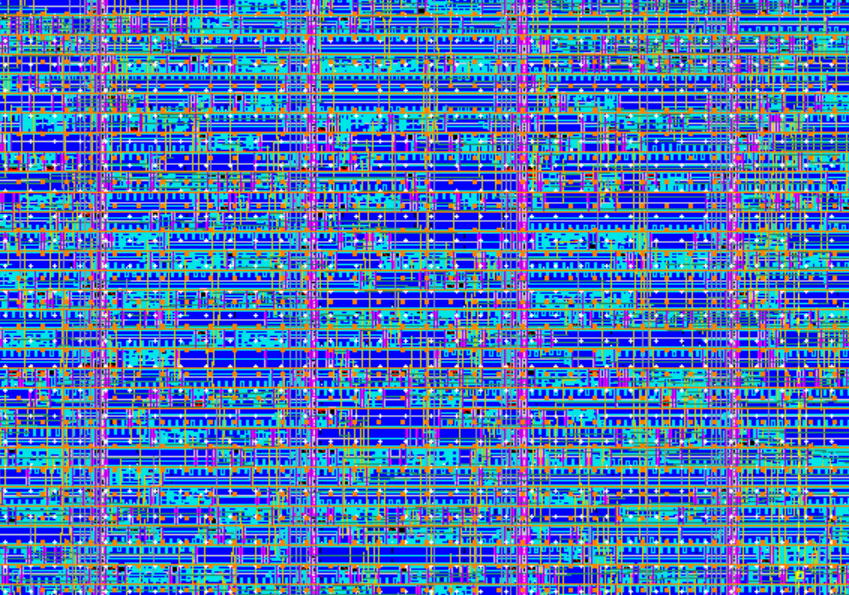

物理设计阶段

物理设计采用tcl脚本,workflow分为:

- init_design:变量的命名和文件的导入

- flat_dp:floorplan和电源网松约束

- place_opt:布局优化

- clock_opt_cts:时序优化(时钟树部分)

- clock_opt_psyn:时序优化(物理部分)

- clock_opt_route:时序优化(布线部分)

- route:布线

- route_opt:布线优化

- chip_finish:确定初稿

- metal_fill:填入填充单元,完成设计

- signoff_drc:signoff前的drc,lvs检查

- outputs:gds版图生成

目前经过各项脚本参数(IOpad布局,电源网参数)的设置,最新版图已通过drc和lvs检验。

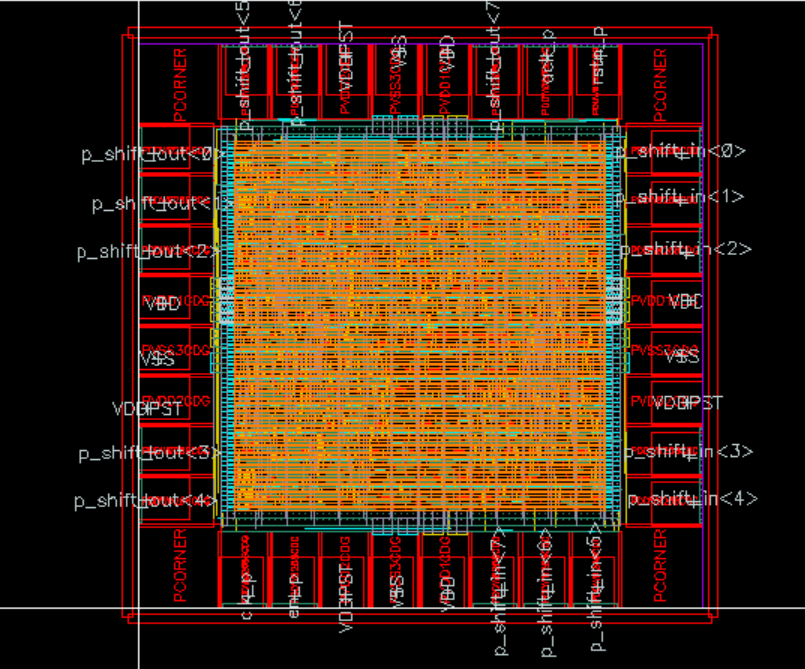

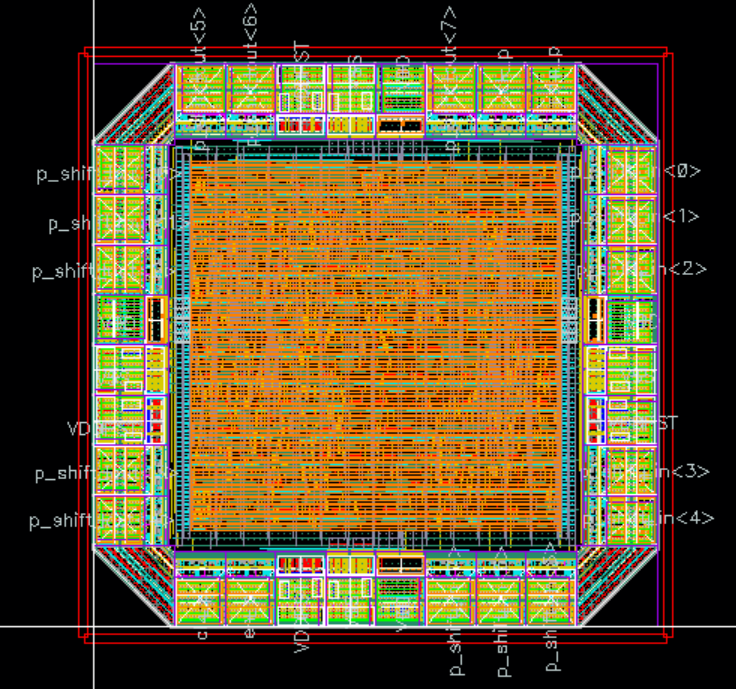

release阶段

icc gds生成后,需要在cadence virtuoso上完成bonding pad和guard ring的手工版图添加,并在mentor calibre上进行DRC, ant, LVS验证,全部通过后即可递交foundry。

pad:

inside:

流片后验证

TBD